I chip del futuro saranno roventi: perché e quali sono le soluzioni per evitarlo

Con l'aumento della densità dei transistor nei chip, il calore generato rappresenta una sfida crescente da affrontare. James Myers di Imec ha analizzato su IEEE Spectrum i possibili scenari funesti e le contromisure possibili in quella che definisce l'era del "CMOS 2.0".

di Manolo De Agostini pubblicata il 19 Aprile 2025, alle 08:01 nel canale ProcessoriSu IEEE Spectrum è stato pubblicato un interessante articolo firmato da James Myers, responsabile del programma System Technology Co-Optimization di Imec, intitolato "I chip del futuro saranno più caldi che mai".

Nell'articolo si analizza come, dopo decenni di progressi seguendo i dettami della "Legge di Moore" - secondo la quale il numero di transistor raddoppia all'incirca ogni due anni - la crescente densità e potenza dei chip si stia scontrando sempre più con il problema della dissipazione del calore.

Il nodo principale è legato al superamento del cosiddetto Dennard scaling (da Robert H. Dennard), secondo cui, riducendo la dimensione dei transistor, la loro densità di potenza rimane costante: l'energia consumata è proporzionale all'area del transistor e sia la tensione che la corrente diminuiscono con la lunghezza del dispositivo.

A metà degli anni 2000, tuttavia, ulteriori riduzioni di tensione sono diventate impraticabili senza compromettere il funzionamento dei transistor. Nonostante ciò, la densità dei transistor ha continuato ad aumentare, determinando un incremento della densità di potenza e, di conseguenza, una maggiore generazione di calore.

L'aumento di compattezza e potenza ha reso la gestione termica una sfida centrale per l'industria dei semiconduttori. Secondo Myers, è necessario un nuovo approccio per prevedere e affrontare l'impatto dell'evoluzione tecnologica sulla generazione e la dissipazione del calore.

Insieme ai suoi colleghi, ha sviluppato un framework simulativo basato su tool EDA standard e open source, integrati con soluzioni proprietarie, che consente di "esplorare rapidamente l'interazione tra la tecnologia dei semiconduttori e i sistemi che la utilizzano". I risultati ottenuti finora evidenziano la necessità di nuove soluzioni, "tra cui nuovi modi di progettare chip e sistemi, se vogliamo che riescano a gestire il calore".

Se oggi si fa affidamento su sistemi di raffreddamento ad aria e a liquido, Myers avverte che "né le ventole né i dissipatori a liquido saranno all'altezza delle soluzioni basate sui processi più piccoli che arriveranno in futuro".

I transistor GAAFET si apprestano a sostituire i FinFET tra la fine di quest'anno e il prossimo, mentre si lavora già ai CFET (transistor a effetto di campo complementari) per gli anni successivi (intorno al 2030). I GAAFET sostituiscono le alette degli attuali FinFET con una pila di fogli orizzontali, mentre i CFET portano questa architettura all'estremo, impilando verticalmente più fogli e suddividendoli in due dispositivi, posizionando due transistor nello stesso spazio occupato da uno solo.

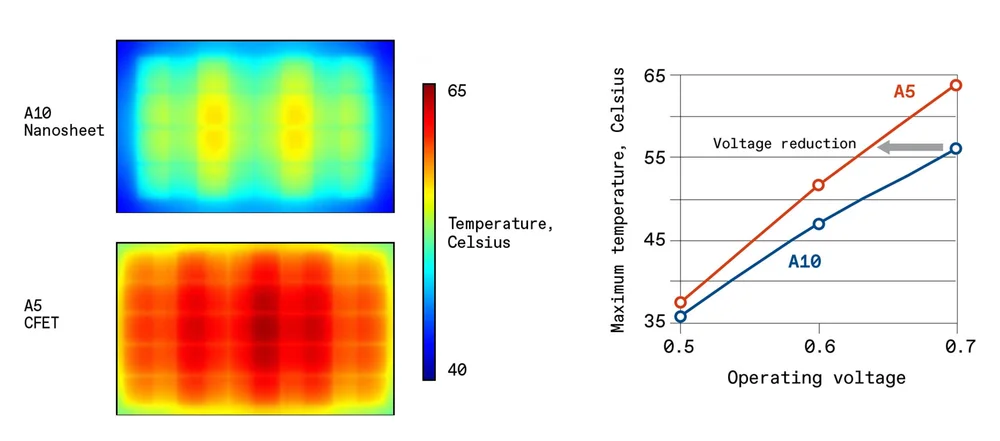

Myers e colleghi hanno analizzato una futura versione di transistor GAAFET realizzata con processo A10 (10 Angstrom, 1 nanometro) e una versione CFET basata su processo A5 (0,5 nm). Ebbene, "le simulazioni dei nostri progetti di prova hanno mostrato che la densità di potenza nel nodo A5 è dal 12 al 15% superiore rispetto all'A10. Questa maggiore densità comporterà, a parità di tensione operativa, un aumento di temperatura di circa 9 °C".

Nei datacenter, dove operano centinaia di migliaia di chip, un aumento di 9 °C per dispositivo può fare "la differenza tra un funzionamento stabile e una fuga termica, quel temuto ciclo di feedback in cui l'aumento della temperatura incrementa la potenza dissipata, che a sua volta incrementa la temperatura, fino a quando i meccanismi di sicurezza non spengono l'hardware per evitare danni permanenti", scrive Myers.

Come affrontare il problema? Una soluzione potrebbe venire dal raffreddamento microfluidico, che prevede minuscoli canali incisi sul chip attraverso cui far circolare un liquido refrigerante. Altre opzioni includono il jet impingement, in cui un fluido viene spruzzato ad alta velocità sulla superficie del chip, e il raffreddamento a immersione, dove l'intero circuito stampato è in bagno di liquido refrigerante.

Sebbene promettenti, queste soluzioni potrebbero non essere praticabili in tutti i contesti. Nei dispositivi mobili, ad esempio, si è vincolati da dimensioni, peso, autonomia e dal rischio di surriscaldamento a contatto con l'utente. Nei datacenter, invece, l'aggiornamento dell'infrastruttura di raffreddamento a ogni nuova generazione di chip farebbe esplodere i costi.

Alcuni approcci agiscono a livello di sistema. Uno consiste nell'installare sensori termici attorno al chip: al superamento di una soglia critica, i sensori attivano una riduzione di tensione e frequenza per limitare il consumo e quindi la temperatura. Tuttavia, il rovescio della medaglia è una significativa riduzione delle prestazioni.

Un altro approccio, noto come thermal sprinting, è utile per le CPU multicore dei server: consiste nell'utilizzare un core alla massima potenza finché non si surriscalda, per poi passare l'esecuzione a un altro core mentre il primo si raffredda. Questo migliora le prestazioni in scenari single-thread, ma può causare inficiare le prestazioni con carichi multi-thread.

Queste soluzioni richiedono un attento bilanciamento tra prestazioni e dissipazione. I progettisti devono conoscere in dettaglio la distribuzione dell'energia sul chip, i punti caldi (hotspot), la posizione ottimale dei sensori e i tempi di raffreddamento. Tuttavia, anche i progettisti più esperti avranno presto bisogno di soluzioni ancora più sofisticate.

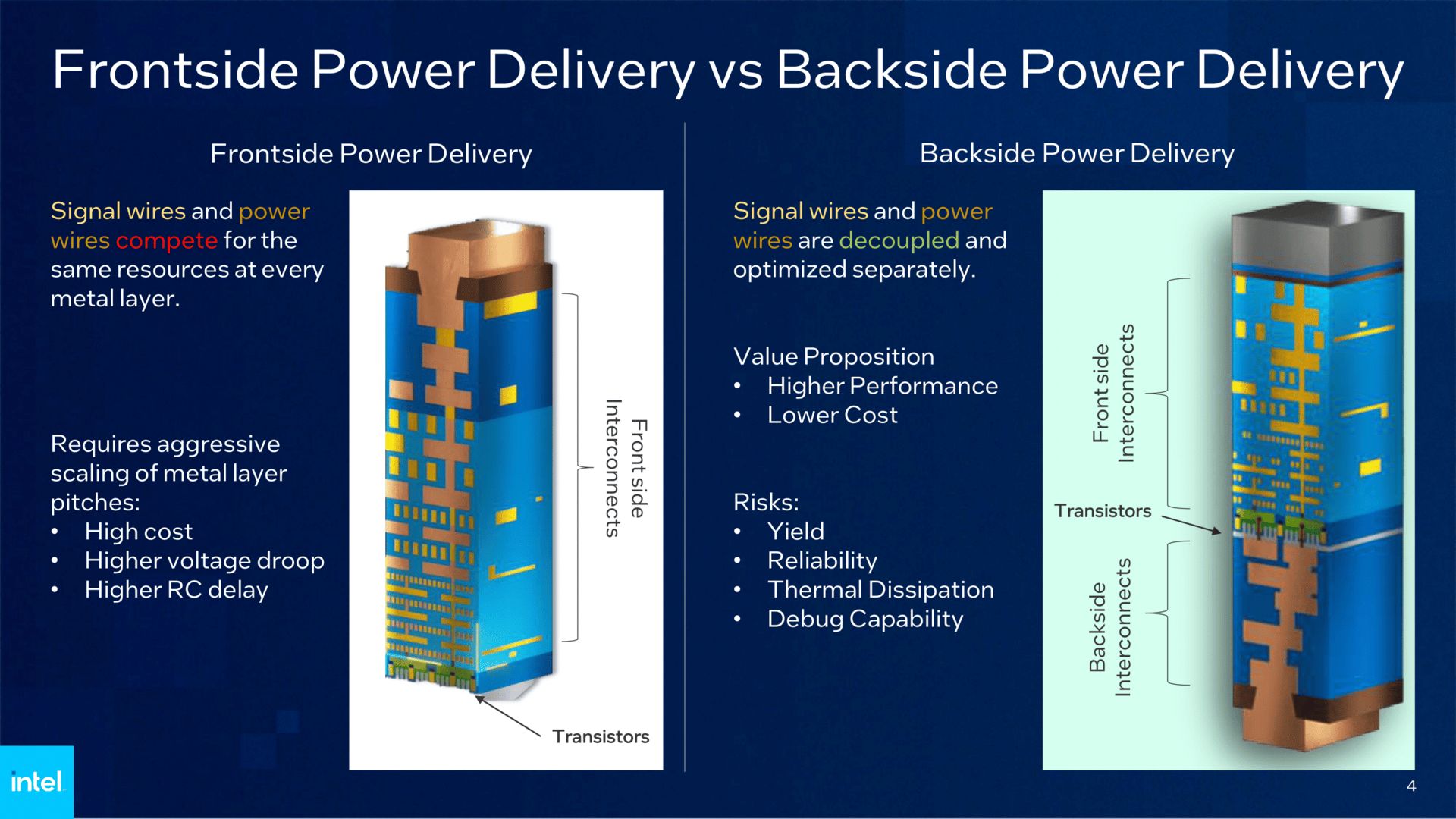

Una strada promettente è l'integrazione di nuove funzionalità sul lato posteriore del wafer (backside), inizialmente pensata per migliorare la distribuzione dell'alimentazione e le prestazioni, ma con potenziali benefici anche in termini di gestione termica.

Imec prevede diverse tecnologie backside che potrebbero permettere ai chip di funzionare a tensioni inferiori, riducendo la generazione di calore. La prima è la Backside Power-Delivery Network (BSPDN), che sposta le linee di alimentazione dalla parte anteriore a quella posteriore del chip. Tutte le principali fonderie avanzate prevedono di adottarla entro la fine del 2026.

Le prime dimostrazioni mostrano che tale soluzione riduce la resistenza elettrica, avvicinando l'alimentazione ai transistor: una resistenza minore implica minori perdite di tensione e, quindi, un funzionamento a tensioni inferiori, con conseguente riduzione della densità di potenza e della temperatura.

Successivamente, si prevede l'integrazione di condensatori ad alta capacità sul lato posteriore, utili a mitigare le oscillazioni di tensione causate dall'induttanza del circuito stampato e del package. La loro vicinanza ai transistor consente una risposta più rapida ai picchi di tensione, favorendo ulteriori riduzioni di tensione e temperatura.

Infine, verranno introdotti regolatori di tensione integrati (Integrated Voltage Regulators, IVR) sul retro del chip, in grado di garantire una regolazione ancora più precisa.

Queste innovazioni comportano però dei compromessi. L'assottigliamento del substrato di silicio necessario per integrare le tecnologie backside può ridurre la capacità di dissipazione termica, creando nuovi hotspot. "La nostra simulazione di un SoC server a 80 core ha rilevato che le reti BSPDN possono aumentare le temperature nei punti più caldi fino a 14 °C", afferma Myers.

Insomma, questi sviluppi che rientrano in quella che Imec definisce l'era del "CMOS 2.0" richiedono ulteriori indagini man mano che le tecnologie evolvono. Myers conclude sottolineando che, per quanto utili, le strategie software di gestione termica sono spesso imprecise e penalizzano le prestazioni più del necessario. Per questo propone un approccio olistico, la System Technology Co-Optimization, che integra progettazione di sistema, layout fisico e tecnologia di processo in un percorso unificato.

Solo promuovendo la collaborazione tra discipline e sfruttando strumenti di simulazione avanzati, l'industria potrà anticipare e affrontare con successo le sfide termiche presentate dai chip del futuro.

Lenovo ThinkPad X9-14 Aura Edition: leggero e sottile per i professionisti

Lenovo ThinkPad X9-14 Aura Edition: leggero e sottile per i professionisti REDMAGIC 10 Air: potenza da gaming in un corpo leggero e moderno. Recensione

REDMAGIC 10 Air: potenza da gaming in un corpo leggero e moderno. Recensione Insta360 X5: è sempre la regina delle action cam a 360 gradi. Recensione

Insta360 X5: è sempre la regina delle action cam a 360 gradi. Recensione Intel: il nuovo CEO annuncia azioni forti, ma per ora nessun licenziamento di massa

Intel: il nuovo CEO annuncia azioni forti, ma per ora nessun licenziamento di massa La missione Shenzhou-20 ha effettuato il docking con la stazione spaziale cinese Tiangong

La missione Shenzhou-20 ha effettuato il docking con la stazione spaziale cinese Tiangong Xbox Cloud Gaming arriva sulle TV LG: verifica se il tuo televisore è compatibile

Xbox Cloud Gaming arriva sulle TV LG: verifica se il tuo televisore è compatibile Stellantis: batterie allo stato solido in arrivo il prossimo anno, ricarica in 18 minuti

Stellantis: batterie allo stato solido in arrivo il prossimo anno, ricarica in 18 minuti Effetto dazi, Logitech alza i prezzi fino al 25% negli USA: non è la sola tra aumenti e fuga

Effetto dazi, Logitech alza i prezzi fino al 25% negli USA: non è la sola tra aumenti e fuga Fondazione Carisbo entra in BI-REX. Obiettivo: accelerare e incubare startup

Fondazione Carisbo entra in BI-REX. Obiettivo: accelerare e incubare startup Dal 20 giugno 2025 arriva l'eco-label UE su smartphone e tablet: cosa cambia per i consumatori e venditori

Dal 20 giugno 2025 arriva l'eco-label UE su smartphone e tablet: cosa cambia per i consumatori e venditori Ionity installerà le prime colonnine Megawatt dell'italiana Alpitronic

Ionity installerà le prime colonnine Megawatt dell'italiana Alpitronic Realme GT7 ufficiale: specifiche da top di gamma a un prezzo super competitivo

Realme GT7 ufficiale: specifiche da top di gamma a un prezzo super competitivo Firefly arriva in Europa: si parte da 23.500 euro

Firefly arriva in Europa: si parte da 23.500 euro GeForce RTX 50: se avete acquistato una Gigabyte, controllate che il gel termico non stia colando

GeForce RTX 50: se avete acquistato una Gigabyte, controllate che il gel termico non stia colando 11 bit studios ha annunciato Frostpunk 1886: un remake in UE5 che andrà oltre la grafica

11 bit studios ha annunciato Frostpunk 1886: un remake in UE5 che andrà oltre la grafica Con NUS Enterprise Volume Agreement Nutanix semplifica la gestione di grandi volumi di dati

Con NUS Enterprise Volume Agreement Nutanix semplifica la gestione di grandi volumi di dati  STMicroelectronics: risultati in calo nel primo trimestre 2025, ma il CEO resta fiducioso nella ripresa

STMicroelectronics: risultati in calo nel primo trimestre 2025, ma il CEO resta fiducioso nella ripresa

13 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoBeh viste le 5000 , si puo dire che le 4000 erano già pronte al futuro

Altre opinioni da boomer ne abbiamo?

l'IA è come la bomba atomica, si stava meglio senza , ma se esiste è meglio averla che non averla

Questo è pur sempre un sito di appassionati, non di ingegneri del MIT. L'articolo è scritto in modo da essere comprensibile a tutti, ridurlo a chiacchiere da bar è denigrare il lavoro di chi l'ha scritto con passione e professionalità. Manolo scrive per testate come questa penso da più di 20 anni. Ricordiamoci il rispetto please.

Intendi semplicemente l'Artic Silver 5?

saranno anche "da boomer", come piace dire a te che sei ciovane, ma la realtà è quella

a cosa serve all'uomo della strada la IA ??

nel concreto: A NULLA

quindi lasciamo l'immensa potenza di calcolo a disposizione della Ricerca e a chi ne ha davvero bisogno.

se poi a te piacciono le notizie in cui "si fondono le gpu per le troppe richieste..."

ma saranno state le troppe richieste di Ricerche Scientifiche, mica richieste idiote di immagini idiote fatte da persione idiote... nooooooo

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".