|

|||||||

|

|

|

|

|

|

Strumenti |

|

|

#31101 |

|

Senior Member

Iscritto dal: Feb 2012

Città: Torino

Messaggi: 534

|

"Nuovi" rumors riportati recentemente sul thread del forum di overclock.net dedicato a ZEN:

"If this capability to fuse and process larger instructions is carried over to Zen it would enable the two 256-bit FMAC units 4 128-bit pipes to fuse and process 512bit AVX instructions. Which would make the core compatible with Intels AVX512 instruction set extension. Which is currently only supported by Intels Knights Landing Xeon Phi microarchitecture. The wider floating point unit also means that Zen will be able to process less complex instructions at double the rate of Steamroller A massive boost in floating point performance, an area where AMD had historically excelled in with Phenom II and prior CPUs." Se AMD implementerà anche in ZEN la possibilità di configurare dinamicamente le pipe della FPU allora le nuove CPU sarebbero davvero competitive offrendo "paradossalmente" più di quanto Intel proponga oggi sulle sue attuali CPU.

__________________

"E' più ragionevole credere in Babbo Natale che nel beta di un transistor" FX6300@4700MHz, Noctua U14S, Asus M5A99FX PRO R2, 2x4GB Corsair 2133MHz CL9, Sapphire R9 270X 2GB Dual-X, CM 690 II, Corsair HX650, Crucial MX500 500GB, Win 10 Dell Vostro V131, Core i5 2430M@2.4GHz, 8GB DDR3, Samsung 840 EVO 250GB, Win 7 Pro x64 |

|

|

|

|

|

#31102 | |

|

Senior Member

Iscritto dal: Oct 2003

Città: Milano

Messaggi: 4054

|

Quote:

considerando il primo athon dualcore, unire le risorse dei due core in un unico supercore, in grado di avere un ipc elevatissimo quando gestisce solo un thread ed un ipc cmq alto quando ne gestisce due. poi si può anche aggiungere l'smt, e ne gestisce 4. ne risulterebbe un'architettura a moduli + CMT. ho intuito? |

|

|

|

|

|

|

#31103 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Io ho capito altro.

secondo la mia interpretazione: 1) Per Paolo HT dovrebbe essere gestito a livello di modulo, nel senso se devo gestire 12 thread, carico 6 su un modulo, e 6 nell'altro. Sarebbe penalizzante secondo Paolo usare un modulo al 100% (8 thread) e quell'altro solo con 4 threads. 2) Questo sarebbe dovuto alla condivisione della cache (l3 e non l2 come riportato da Paolo). Gli faccio notare che nel caso in cui il core1 aspetta un dato elaborato dal core 7, questo deve passare attraverso la memoria RAM. La mia personale opinione, è che il SO deve continuare a gestire la cpu come ha sempre fatto. Caricare il più possibile in maniera uniforme i core. Una soluzione alla Paolo (preferenza per il carico su un modulo) penalizza questo tipo di approccio (e in effetti è alternativo, ma vedi quante idee ha Paolo? Semplicemente mostruoso), ma ha un suo perchè. Chi avrà ragione? Ultima modifica di tuttodigitale : 06-10-2015 alle 14:20. |

|

|

|

|

|

#31104 | |

|

Senior Member

Iscritto dal: Jul 2015

Messaggi: 4728

|

Quote:

Paolo parlava del salto del th in esecuzione (per esempio dallo stadio 10 della pipeline 1 del core 0 allo stadio 11 della pipeline 3 del core 2) ed il mio esempio era solo per spiegare (e ripeto terra terra) che un'istruzione in pipeline non può essere fatta uscire da uno stadio per entrare in uno stadio consecutivo di una pipeline diversa. avrei scritto meglio: Nello stadio 1 (fech) l'istruzione viene caricata dalla memerio nel 2 viene codificata nel 3 vengono caricati gli operandi nel 4 viene eseguito il calcolo nel 5 viene scritto il risultato in ram( cache). Quindi passare dallo stadio 2 di una pipeline allo stadio 3 della pipeline di un altro core è non fattibile, ma bisogna ripetere il processo dall'inizio. Questo volevo spiegare, perché 2+2/2 non è un'istruzione, ma due istruzioni separate (che alcune volte possono essere accorpate ed eseguite in singola passata, altre volte hanno bisogno di più passate dipendente dalla complessita totale e dalla logica della cpu che la esegue) |

|

|

|

|

|

|

#31105 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 30510

|

Mi sono spiegato male, colpa mia.

Partiamo dalla L2 che comunque deve contenere le istruzioni dei TH. In Intel abbiamo 1 L2 e a cascata tutte le vie per gestire i 2 TH su 1 core. In AMD, abbiamo sempre 1 L2, ma siccome condivisa nel modulo per 4 core, l'SMT potrebbe funzionare non sulla disponibilità di 1 core, ma su quella del modulo. Ora, se 1 core nella media lavorasse al 75%, il TH "parallelo" avrebbe a disposizione il 25%. Siccome la L2 in Zen è condivisa e praticamente serve tutti e 4 i core, l'SMT credo che anziché portare al 100% 1 core potrebbe portare al 100% il modulo Ora, supponiamo che un 4 core Intel + SMT debba risolvere 5TH. 4 TH avrebbero la priorità e elaborati al 75%, ma il 5° avrebbe a disposizione il 25% di 1 core, e risulterebbe richiedere 4 volte in più di tempo rispetto agli altri TH e di fatto 3 core che non sfrutterebbero l'SMT. Se fosse possibile che l'SMT di AMD sfruttasse il modulo e non il singolo cote, il 5° TH potrebbe lavorate anche al 100% (senza dare la priorità ad altri core) semplicemente perché ogni stallo di qualsiasi core verrebbe sfruttato per portare avanti quel TH senza che poi un TH venga impostato a priorità differenti. Io faccio fatica a spiegare, ma se in Intel il 2° TH lavora al 25% e sta al 75% ad aspettare il primo TH, quei cicli 3 x 25% non potrebbero essere spostati sugli altri core? P.S. Lungi da me interpretazioni di bandiera, io prospetto solamente cosa potrebbe avere l'SMT di AMD di diverso fa Intel. Fermo restando, anche letto gli ultimi post, che le potenze sulla carta possono essere superiori quelle di Zen, ma dalla carta al silicio, dubito sull'efficienza AMD.

__________________

7950X - X670E Asrock PG - Aio 360 Thermaltake - RS/DU TDP max 230W - CB23 39.117 https://ibb.co/M9j2bV7 - CPU-Z 815/16427 https://valid.x86.fr/jdgu90 - No overdrive - OCBench NO RS CB23 40.697 https://ibb.co/W0qnRQB - Codifica video https://ibb.co/Jm5Zj0M Ultima modifica di paolo.oliva2 : 06-10-2015 alle 14:55. |

|

|

|

|

|

#31106 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Quote:

Piedone, ero rimasto un pochino perplesso quando hai risposto ad un commento alterandone il significato. Tutto a posto: la prossima vedrai che mi correggerai tu.

|

|

|

|

|

|

|

#31107 | |

|

Senior Member

Iscritto dal: Jul 2015

Messaggi: 4728

|

Quote:

Se un th utilizza 3 pipeline su 4 al secondo th rimane una sola pipeline 25% perché nel th gestito dall'smt non viene concesso l'uso delle 4 pipe rimanenti (su 4 core 3 pipe per ogni th + 5° core virtuale dalla fusione delle pipeline rimanti, cioè una per core)? Oppure se una pipeline stalla in attesa di un dato (significa che un blocco della pipeline è in attesa di un evento in fase di elaborazione e quindi impedisce alla pipeline di proseguire con il suo flusso) spostare il th in coda nella pipeline su un'altra pipeline di un altro core? l'smt sfrutta i tempi morti delle pipeline (praticamente un th aspetta un dato per poter iniziare una nuova operazione), ed in questi intermezzi che il core virtuale impegna la pipeline con un altro th. In media l'uso delle pipeline è di 2,7 per processo, ma può variare e di molto da processo e processo. Fin'ora abbiamo assistito alla gestione dinamica a livello di core delle risorse, nel tuo caso stai chiedendo se sia possibile avere una gestione dinamica della gestione dei core a livello di modulo e cioè passare da 4+4ht a 4+1ht ma sempre sfruttando il 100% delle pipeline a seconda del carico. Giusto? @Tuttodigitale Figurati, non hai mica torto, ho cercato di spiegare un concetto senza entrare nella complessita propria delle cpu (che al 100% conosci molto meglio di me) e questo mi ha portato a fare un esempio non veritiero (anche se credo più facile da capire). Anche se sono un appassionato di cpu molte cose mi sono ostiche da capire e cerco di farmi esempi elementari (per similitudine) per cercare di comprendere meglio. Ultima modifica di Piedone1113 : 06-10-2015 alle 15:37. |

|

|

|

|

|

|

#31108 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Quote:

le unità di esecutive (10) sono indipendenti. Se ci possono essere effettivi dubbi sull'effettiva utilità nel ST (i colli di bottiglia sono altrove), con due thread è effettivamente pensabile che il SMT possa effettivamente dare di più. Il back-end di ZEN sembrerebbe bello corposo (sarebbe comunque da valutare la reale potenza delle ALU, tanto che il SMT-4 non è improbabile, sempre secondo me. ecco il front-end di haswell.

Ultima modifica di tuttodigitale : 06-10-2015 alle 15:42. |

|

|

|

|

|

|

#31109 | |

|

Member

Iscritto dal: Apr 2013

Messaggi: 247

|

State facendo un casino con sta storia delle pipeline che non avete idea

Quote:

|

|

|

|

|

|

|

#31110 | ||

|

Senior Member

Iscritto dal: Mar 2012

Messaggi: 978

|

Quote:

Quote:

__________________

Case Xigmatek Utgard CPU FX-8320E@4200 Mobo Asus Sabertooth 990FX Dissipatore Zalman 9900Led Ram G.Skill 4GB 1600 MHz VGA R9 270 Dual-X PSU XFX ProSeries 450W

"la conoscenza è il nostro scopo supremo" Ultima modifica di .338 lapua magnum : 06-10-2015 alle 16:26. |

||

|

|

|

|

|

#31111 | |

|

Senior Member

Iscritto dal: Sep 2005

Messaggi: 2177

|

Quote:

__________________

__________ Configurazione: Mainboard Gigabyte G1.Sniper A88X (rev. 3.0) ; APU A10 7850K ; HDD Western Digital SATA III WD Blue 1 TB ; Ram Corsair 1866 mhz 16 gb ; OS Seven premium 64 bit |

|

|

|

|

|

|

#31112 | ||

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Quote:

Quote:

In BD/PD ci sono 4 pipeline per la fpu contro le 3 di Steamroller (per entrambi 2 FMAC). P0 f.p. addition, multiplication, division, integer vector multiplication P1 f.p. addition, multiplication, division, shuffle, shift, pack P2 integer vector addition, boolean, move P3 integer vector addition, boolean, move, store la p2 è stata eliminata in Steamroller Ultima modifica di tuttodigitale : 06-10-2015 alle 21:00. |

||

|

|

|

|

|

#31113 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 30510

|

Se posso dire...

Se la potenza di calcolo complessiva di Zen grossomodo fosse simile a quella Intel, ed Intel riesce a sfruttarla con 2 TH, nel senso che il numero pipeline riesce a far lavorare tutte le ALU del core... Perché AMD dovrebbe produrre una potenza superiore? Cioè, o Intel non arriva al 100% ed AMD con SMT 4 si, altrimenti qualche cosa non mi torna. Ma... Io vedo che l'esperienza di AMD con l'acquisizione di ATI è notevole ed Intel fatica il recupero seppur con pozzi di sodi e quant'altro.... Allo stesso modo, trovo incomprensibile ed impossibile che AMD possa realizzare un SMT ancor più complesso di quello Intel, con tutto il contorno di cache, predizione e simili, e dalla carta al silicio con tutti i problemi sia di "compatibilità" da progetto al silicio ed annessi e connessi bilanciamenti TDP dovuto al consumo su un silicio che a tutt'oggi ad essere ottimisti sarebbe in via di sviluppo e quindi ben lontano dal conoscere gli effettivi limiti. BAH... Nei comunicati GF si inquadra un range di funzionamento di Zen tra i 3 e 4GHz, cioè un range di +/- 33%, una vita. Da una parte si arriverebbe a poco più di un 25% rispetto a Pile, dall'altra un 70% in più.

__________________

7950X - X670E Asrock PG - Aio 360 Thermaltake - RS/DU TDP max 230W - CB23 39.117 https://ibb.co/M9j2bV7 - CPU-Z 815/16427 https://valid.x86.fr/jdgu90 - No overdrive - OCBench NO RS CB23 40.697 https://ibb.co/W0qnRQB - Codifica video https://ibb.co/Jm5Zj0M |

|

|

|

|

|

#31114 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Quote:

Ma non si sa niente sul numero di stages? |

|

|

|

|

|

|

#31115 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

Quote:

Dresdenboy ha parlato di una riduzione generica di stadi della pipeline, ma come al solito sono solo speculazioni. Ultima modifica di Ren : 07-10-2015 alle 11:49. |

|

|

|

|

|

|

#31116 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 30510

|

Quote:

Sempre a spannella, da un 32nm ad un 14/16nm si avrebbe un -50% di TDP, quindi da un 8350 X8 si passerebbe tranquillamente ad un X16. Un Zen X8 con +70% di IPC concederebbe un X12 nei 125W, un X8 nei 95W ci starebbe. Da tenere presente che BD ha un TDP alto non per l'architettura, ma per il silicio. Considerando un 8350 a 95W, un Zen X8 a 95W ci starebbe alla stragrande. Comunque, a me piacerebbe se possibile quantificare un Zen con e senza SMT (se disabilitabile), perché si avrebbe il metro preciso di quanto sarebbe potuto andare il CMT sul 32nm, perché il CMT è una cosa, la lunghezza pipeline un'altra e tutta la differenza (per me abnorme) era tutta nel 32nm. Anche il discorso IPC di BD pra di Zen è stato strettamente dipendente al silicio, vedi FX no Steamroller e no Excavator, ma non possiamo manco escludere che sia ST che Ex siano stati gambizzati per rientrare in determinati TDP.

__________________

7950X - X670E Asrock PG - Aio 360 Thermaltake - RS/DU TDP max 230W - CB23 39.117 https://ibb.co/M9j2bV7 - CPU-Z 815/16427 https://valid.x86.fr/jdgu90 - No overdrive - OCBench NO RS CB23 40.697 https://ibb.co/W0qnRQB - Codifica video https://ibb.co/Jm5Zj0M |

|

|

|

|

|

|

#31117 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4095

|

Quote:

ho come l'impressione che in quella slide AMD, si riferisca si alle prestazioni di un core XV vs ZEN+SMT, ma solo per quello che attiene al calcolo intero. (per amd i core sono i cluster integer). imho, un core ZEN con HT potrebbe andare circa 80-90% di un modulo SR nei calcoli integer, e un buon 10-20% in più nel FP. Non mi sembra affatto male. |

|

|

|

|

|

|

#31118 | |

|

Member

Iscritto dal: Apr 2013

Messaggi: 247

|

Quote:

|

|

|

|

|

|

|

#31119 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 30510

|

Quote:

Se poi AMD farebbe un Zen 5960X

__________________

7950X - X670E Asrock PG - Aio 360 Thermaltake - RS/DU TDP max 230W - CB23 39.117 https://ibb.co/M9j2bV7 - CPU-Z 815/16427 https://valid.x86.fr/jdgu90 - No overdrive - OCBench NO RS CB23 40.697 https://ibb.co/W0qnRQB - Codifica video https://ibb.co/Jm5Zj0M |

|

|

|

|

|

|

#31120 |

|

Senior Member

Iscritto dal: Apr 2011

Città: Funky Town

Messaggi: 3371

|

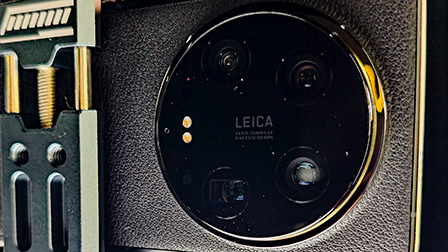

Table FP, Bulldozer and Zen

Comparativa tratta dal profilo twitter di dresdenboy

saranno obsolete, ma a me fa (molto) piacere rivedere le X87

__________________

......... |

|

|

|

|

| Strumenti | |

|

|

Tutti gli orari sono GMT +1. Ora sono le: 08:54.