[Thread Ufficiale V3.0]

AMD K10 Phenom Quad/Triple/Dual Core

Questo thread è di informazione sulle nuove CPU K10 e derivati, compreso i vari chipset e nuovi progetti a lungo o breve termine di AMD, legati naturalmente alla tecnologia K10.

Regolamento

- non sono ammessi notizie o commenti sull'andamento finanziario ( compreso i titoli quotati in borsa ) o di mercato da parte di AMD e/o Intel.

- non sono ammessi commenti catastrofici o comunque in grado di generare FLAME

- non sono graditi commenti stile Fanboy sia da parte AMD sia da parte Intel

- non sono ammessi commenti sulle prestazioni della GPU R600/RV670/RV770/R700 o derivati, tranne per discutere del progetto FUSION

- non sono ammessi commenti sul modulo TPM o sull'argomento "Palladium" in quando la scelta di utilizzare questo chip sarà unicamente del produttore di schede madri

- non sono ammessi post stile "consigli per gli acquisti" o consigli o suggerimenti per la scelta di un nuovo hardware

- non sono ammessi discussioni prolungate sulle CPU Athlon64/X2

- Cerchiamo di limitare al minimo gli argomenti OT, se proprio non ce la fate comunicate attraverso i messaggi privati

- Per evitare di appesantire eccessivamente il Thread le immagini postate non dovranno superare la risoluzione 800X600 pixel

ATTENZIONE:

Per evitare che i post OT e AMD vs Intel inquinino il Thread lascio l' avvertimento del moderatore di sezione andw7:

Quote:

|

Originariamente inviato da andw7

ripeto, per tutti: finora il thread è andato via abbastanza liscio e con argomenti e contenuti interessanti. cerchiamo di continuare così e di non farlo diventare come "Aspettando R600" e simili.

a me non costa niente far fioccare le sospensioni, però sarebbe un vero peccato.

Che serva per tutti. dalla prossima volta le sospensioni andranno dalla settimana in su

|

Indice del Thread:

Prima pagina:

Regolamento / AMD K10 nel Dettaglio!

Seconda Pagina:

AMD K10 Phenom: I modelli CPU e Chipset AMD/Nvidia/SIS socket AM2+/1207+ e AM3!

Terza pagina:

AMD K10 e oltre: Il futuro e i nuovi progetti di AMD!

Quarta Pagina:

Lista schede mamme AM2 e bios compatibili con i K10 socket AM2+!

Quinta pagina:

Lista schede mamme AM2+ compatibili con le CPU TDP a 125W!

Sesta Pagina:

AMD K10: Benchmark, News e/o indiscrezioni dalla rete!

Settima Pagina:

AMD K10: Thread Ufficiali Schede mamme AM2+, FAQ, prezzi, date di uscita!

---------------------------------

Link precedenti Thread Ufficiali AMD K10 Phenom

[Thread Ufficiale] K10 Phenom ( Versione 1.0 )

[Thread Ufficiale] K10 Phenom ( Versione 2.0 )

---------------------------------

K10 nel dettaglio!

- nuove estensioni SSE4A;

- supporto SSE dual 128bit, contro quello a 64bit delle attuali versioni di processore Athlon 64 e Opteron

- scheduler in virgola mobile a 36 vie, con ampiezza passata da 64 a 128 bit;

- raddoppio della bandwidth delle instruction fetch, passando da 16 a 32 bytes per ciclo di clock;

- nuova generazione di bus HyperTransport, revision 3.0, inizialmente solo per i processori desktop e in seguito anche sulle soluzioni server;

- raddoppio del bus tra le cache L1 e L2, passato da 128bit a 256bit (2 bus indipendenti da 128bit);

- prefetcher modificati per fornire dati direttamente alla cache L1;

- aggiunta di un prefetcher DRAM integrato nel memory controller;

- memory controller ottimizzato, specificamente sviluppato per sfruttare la presenza di 4 core;

- tecnologia di virtualizzazione migliorata;

- gestione del risparmio energetico più avanzata che in K8.

- Passaggio di molte istruzioni, anche di tipo intero, da Vector path a directPath: quindi superiori prestazioni sia in decodifica (maggiori istruzioni decodificabili) che in esecuzione (meno macro-ops da eseguire). Molte SSE, sopratutto quelle a 128 bit, sono state declassate, ma anche le CALL e le RET (usate frequentissimamente) e altre istruzioni intere.

- Nuova branch prediction unit per i salti indiretti, espansione delle altre branch prediction unit, return stack espanso e Sideband stack optimizer (libera unità intere dall'esecuzione di operazioni stack: molto utile).

- Controller RAM e cache L3 sullo stesso power plane e con lo stesso PLL. Da impostazioni di default dovrebbero andare ad una frequenza superiore di 200-400 MHz a quella massima del core e con un leggero over volt (solo su socket AM2+). Avendo frequenza e tensione separata, il controller RAM non sarà più un collo di bottiglia durante overclock spinti, potendone abbassare il moltiplicatore e/o modificare la tensione di alimentazione.

- Super forwarding per alcune operazioni floating point e load da memoria.

- Eliminazione delle limitazione di esecuzione di alcune istruzioni floating point su specifiche pipeline: nel k8 alcune istruzioni potevano essere eseguite solo su una pipeline specifica (FADD, FMUL o FSTOR), ora alcune istruzioni sono state modificate in modo da poter usare due o qualsiasi pipeline.

- Nuovi TLB per pagine da 1GB (utili sopratutto per la virtualizzazione).

Le Novità più importanti!

SSE a 128bit

Una delle principali caratteristiche architetturali delle cpu Intel Core 2 è data dalla gestione delle istruzioni SSE a 128bit; questa caratteristica permette alle soluzioni Intel di essere sensibilmente più veloci delle soluzioni AMD64.

AMD è corsa ai ripari con il nuovo core K10, inserendo anche in questa architettura il supporto SSE a 128bit e raddoppiando, di fatto, tutti gli elementi ad esso collegati. Se con i processori della famiglia K8 AMD può eseguire due operazioni SSE per ciclo di clock, con execution unit ampie 64bit, con K10 AMD può eseguire sempre due operazioni SSE per ciclo di clock, ma con execution unit da 128bit. La conseguenza diretta è che in presenza di un'istruzione SSE a 128bit di ampiezza una execution unit di K10 necessita di un solo ciclo di clock per completare l'operazione, mentre K8 deve dividere l'istruzione come se fosse composta da due distinte operazioni da 64bit ciascuna.

L'aver introdotto execution unit SSE a 128bit ha spinto AMD a raddoppiare sia la bandwidth delle instruction fetch, passata da 16bit a 32bit per ciclo di clock, che la bandwidth della data cache, raddoppiata da 2x64bit a 2x128bit loads per ciclo di clock. Per poter fornire i dati alle execution unit in tempo, senza che queste debbano attendere sprecando cicli di clock inutilmente, AMD ha raddoppiato l'ampiezza della bandwidth che collega la cache L2 e il north bridge tra di loro, passando dai 64bit dell'architettura K8 ai 128bit di quella K10.

Non solo: è stata raddoppiata anche la bandwidth tra la cache L1 per i dati e i registri SSE, passando da 2 load a 64bit per ciclo di clock a 2 load a 128bit per ciclo di clock; questo permette di trasferire dalla memoria 128bit per ogni ciclo di clock, saturando completamente e sfruttando appieno tutti i bus raddoppiati rispetto a K8 sino a giungere alle execution unit. Ovviamente anche la bandwidth tra cache L2 e L1 è stata raddoppiata, così da non creare un collo di bottiglia al trasferimento dei dati verso le execution unit.

Lo scheduler per le operazioni in virgola mobile è stato raddoppiato: è sempre del tipo a 36 entry come quello utilizzato nei processori K8, ma con ampiezza passata da 64bit a 128bit. Nelle architetture Core di Intel lo scheduler è a 32 entry a 128bit, ma condiviso tra operazioni di tipo floating point e quelle su numeri interi.

AMD, quindi, con K10 ha operato da un lato per raddoppiare la potenza elaborativa delle execution unit SSE, portandole a 128bit, e dall'altro a fare in modo che i dati possano passare dalla memoria alle cache e da queste alle execution unit così che i 128bit di ampiezza siano sempre completamente sfruttati, evitando che sussistano dei colli di bottiglia.

Hypertransport 3.0

Hyper Transport è una tecnologia sviluppata ( non creata ) da AMD, consiste nel collegamenti punto-punto ad alta velocità per l'interconnessione di

circuiti integrati sulla scheda madre, cosa ben diversa dalla tecnologia con FSB o Front Side Bus usata da Intel. L'ampiezza Hyper Transport 1.0 varia da 4, 8, 16 e 32 bit per una larghezza di banda complessiva di

12.8 GB/second. Ad 8 bit garantisce un'ampiezza di banda di

3,2 Gb al secondo.

Per fare un esempio L'athlon 64 socket 754 ha Hyper Transport a 4x (800mhz), mentre L'athlon 64 socket 939/AM2 e l'opteron socket 940/1207 hanno Hyper Transport a 5x (1000mhz).

Hyper Transport 3.0 introduce significative novità che da un lato migliorano le prestazioni velocistiche complessive, dall'altro aprono spazio ad utilizzi di HyperTransport molto più complessi di quanto non sia stato fatto sino ad ora. Partiamo dai dati puramente velocistici: le nuove specifiche 3.0 prevedono un significativo incremento nella frequenza di clock,

passata dai 1,4 GHz della versione 2.0 agli attuali 2,6 GHz. Di conseguenza, la bandwidth massima teorica disponibile passa dai precedenti

11,2 GBytes al secondo agli attuali 20,8 Gbytes al secondo per ciascun link.

Hyper Transport 3.0 introduce anche un connettore chiamato

HTX (HyperTransport Expansion Slot).

Sviluppato dal consorzio HyperTransport, permette di montare schede di espansione nel sistema che utilizzino proprio HyperTransport, quindi siano

direttamente collegate ai processori. Si può pensare a questo come ad un nuovo bus, alternativo a quello PCI Express ad esempio; in realtà le differenze sono radicali, in quanto HTX permette una

comunicazione diretta tra periferica HTX e processore, oltre che con tutto quello che è collegato attraverso bus HyperTransport, senza dover passare attraverso un controller o un hub montato sulla scheda madre e in grado di impattare sulla latenza.

Altra caratteristica estremamente importante è la possibilità di collegare

server in cluster utilizzando una connessione HyperTransport, mantenendo quindi un collegamento diretto tra i

processori di server diversi e senza dover adottare un sistema di connessione, come Infiniband, che gestisca la trasmissione dei dati tra le macchine.

Il segnale HT può essere trasmesso per lunghezze sino a 1 metro,

senza alcun tipo di perdita di efficienza del segnale

I processori K10 integreranno al proprio interno sino a 4 link Hypertransport a 16bit, contro i 3 attualmente presenti nelle CPU K8.

Questo conferirà superiore flessibilità nella configurazione dei server basati su processori Opteron. I 4 link potranno inoltre essere gestiti come 8 link a 8 bit ciascuno, per configurare sistemi server con un massimo di 8 Socket, corrispondenti a 32 processori fisici nel caso in cui si utilizzino cpu di tipo Quad Core.

Le cpu K10 per sistemi server, meglio note con il nome di Barcelona, adotteranno la tecnologia Hypertransport 1.0 e non quella 3.0. I processori della serie desktop basati su architettura K10, viceversa, passeranno immediatamente alla tecnologia Hypertransport 3.0 grazie all'utilizzo delle piattaforme Socket AM2+, meccanicamente compatibili con i processori Socket AM2 già disponibili in commercio.

Memory controller

Il memory controller delle cpu K10 è integrato all'interno del core e supporterà le memorie DDR2. Mentre il supporto alle memorie DDR3 verrà aggiunto con l'uscita del socket AM3, la quale manterrà il pieno supporto alle DDR2.

Il memory controller ha subito una serie di ottimizzazioni rispetto a quanto visto in K8; i dati che devono essere scritti sulla memoria non vengono ad essa inviati immediatamente, ma memorizzati in un buffer appositamente implementato nel memory controller. Una volta che il buffer raggiunge una determinata soglia di riempimento, i dati vengono inviati tutti alla memoria per essere scritti in essa in modo sequenziale. Alla base di questo approccio troviamo la volontà di evitare di passare da letture a scritture alla memoria, e viceversa, in quanto il passaggio dalla lettura alla scrittura implica alcune penalizzazioni prestazionali; così facendo alcune scritture verso la memoria vengono eseguite sequenzialmente, riducendo il numero di passaggi da scrittura a lettura e viceversa.

Il memory controller delle cpu K10 è sempre a 128bit di ampiezza, esattamente come era per K8; a differenza di quest'ultimo tuttavia il controller è di fatto composto da due controller a 64bit, caratteristica che dovrebbe permettere di ottenere benefici dal punto di vista prestazionale soprattutto nelle versioni di processore quad core. Ogni controller può infatti operare in modo indipendente dall'altro qualora richiesto.

L'indirizzabilità della memoria fisica verrà aumentata sino a 48bit, contro gli attuali 42bit delle cpu K8 in commercio: questo permetterà di gestire un massimo teorico di 256 Terabytes di memoria di sistema per ogni singolo sistema.

Cache L2 e L3

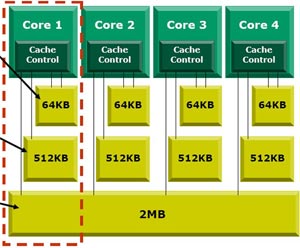

Il K10 in aggiunta alle cache L1 ed L2 AMD ha integrato in queste architetture una cache di terzo livello, o L3, che verrà inizialmente proposta in quantitativo pari a 2 Mbytes ma che potrebbe venir ampliata in successive revision di processore, nel momento in cui saranno disponibili tecnologie produttive più sofisticate di quella a 65 nanometri utilizzata per le prime soluzioni K10.

Le due cache sono di tipo esclusivo, caratteristica già presente nelle precedenti versioni di processore Athlon 64 e Opteron: questo implica pertanto che i dati contenuti nella cache L1 non siano replicati in quella L2, e viceversa.

Le cache L1 e L2 hanno mantenuto la struttura già presente nei processori K8: la cache L1 è associativa a 2 vie e quella L2 associativa a 16 vie. Per la cache L3, infine, AMD ha scelto una struttura di cache associativa a 32 vie.

Nuove funzionalità di risparmio energetico

Il sistema di risparmio energetico implementato nelle architetture Quad Core permette di gestire in modo individuale e indipendente per ciascun core la frequenza di funzionamento, ma non il suo voltaggio che rimarrà identico tra i vari core. Ogni core ha un suo PLL indipendente, ma il voltaggio di alimentazione è gestito in modo diretto per tutti i Core, bloccato su quello richiesto dal core che ha la percentuale di occupazione più alta al momento attuale.

K10 integrerà una logica di gestione dell'alimentazione di processore e memory controller differenziata: per questo motivo, pertanto, cpu e controller memoria potranno ricevere voltaggi differenti in funzione del tipo di carico chiesto in un preciso istante, così da minimizzare il consumo complessivo.

Il fatto che il memory controller abbia un proprio PLL separato da quello del processore, a differenza di quanto integrato con i processori K8 che hanno un solo PLL per cpu e per memory controller, ha permesso di eliminare il problema di avere sincronizzazione perfetta della memoria solo con alcuni moltiplicatori di frequenza. Di conseguenza sarà sempre possibile, con le versioni sia desktop che server, avere ad esempio memoria DDR2-800 sfruttata pienamente a 800 MHz di clock a prescindere dalla frequenza di funzionamento del processore.

Un PLL indipendente per il memory controller permette inoltre di modificare dinamicamente la frequenza di clock di questo componente: qualora il tipo di elaborazioni eseguite non richieda al memory controller di lavorare al pieno delle proprie potenzialità, sarà possibile abbassarne dinamicamente e indipendentemente dai processori la frequenza di funzionamento. Anche questa caratteristica contribuirà al contenimento del consumo di funzionamento di questi processori.

La gestione del risparmio energetico in K10 è andata oltre: alcune parti del processore possono essere di fatto spente in modo indipendente, a seconda del tipo di richiesta fatta dalla specifica applicazione in uso; di fatto a quei componenti inutilizzati viene portata la frequenza di funzionamento a zero, contribuendo nuovamente alla riduzione del consumo complessivo del processore.

Virtualizzazione

Tra le novità che AMD integrerà all'interno dell'architettura K10 segnaliamo alcune innovazioni specificamente legate alla virtualizzazione. Come noto sia Intel che AMD hanno implementato queste tecnologie a livello hardware all'interno delle proprie più recenti cpu, ma con le cpu K10 AMD proporrà alcune innovazioni rispetto all'approccio seguito con le cpu K8.

In un ambiente virtualizzato i processori non possono accedere direttamente all'hardware per indirizzare richieste di particolari indirizzi di memoria da parte del sistema operativo, verso l'indirizzo fisicamente utilizzato dall'hardware. Per limitare l'impatto di questa doppia richiesta l'hypervisor utilizza una tecnologia software chiamata shadow paging, che non ha dalla sua la velocità di esecuzione come punto di forza. All'interno delle cpu K10 è stato inoltre implementato del nuovo hardware che permette di gestire le guest page senza dover chiamare in causa l'hypervisor. Questa nuova tecnica, chiamata Nested Paging, dovrebbe richiedere solo marginali modifiche ai produttori di software di virtualizzazione per poter essere utilizzate, risultando di conseguenza di rapida adozione una volta che le cpu K10 debutteranno in commercio.

I lockup della memoria, in ambiente virtualizzato, verranno gestiti dalle cpu K10 via hardware attraverso Device Exclusion Vector (DEV). Ad ogni macchina virtuale viene associato un determinato quantitavo di memoria fisica; se una macchina virtuale richiede una porzione di memoria ad essa associata, può accedervi; se invece una macchina virtuale richiede una porzione di memoria che ad essa non è associata la richiesta viene bloccata dalle cpu K10 direttamente in hardware, così che questa macchina virtuale non possa andare a modificare la memoria fisica associata ad un'altra macchina virtuale. Le cpu Intel possono fare la stessa cosa, ma con istruzioni software: di conseguenza le prestazioni sono superiori e più elevata la sicurezza complessiva.

In sintesi, AMD ha implementato in K10 varie ottimizzazioni specificamente pensate per ambienti virtualizzati, particolarmente utili quindi nelle versioni di processore destinate ad ambienti server e workstation e che, stando a quanto anticipato da AMD, dovrebbero permettere di ottenere prestazioni superiori in questi ambienti rispetto alle cpu Intel Core 2.